A GaAs DOUBLE-BALANCED DUAL-GATE FET MIXER IC

FOR UHF RECEIVER FRONT-END APPLICATIONS

Kunihiko Kanazawa, Masaru Kazumura, Shutaro Nambu,

Gota Kano, and Iwao Teramoto

Semiconductor Laboratory

Matsushita Electronics Corporation

Takatsuki, Osaka, Japan

ABSTRACT

A double-balanced dual-gate FET mixer has been developed aiming at the application to a front-end circuit of the UHF receivers.

An experimental IC has exhibited a 6 - 8 dB conversion gain without matching over a wide frequency range from 100 MHz to 800 MHz with the well suppressed RF/LO feedthrough by more than 20 dB and third-order intermodulation product of -60 dB.

INTRODUCTION

Implementation of the front-end circuit of the TV tuner is an attractive goal in applying GaAs analog IC's to the consumer area (1). In order to reach this goal many efforts have been devoted so far mainly dealing with low noise wide band amplifier circuits and mixer circuits.

Although the wide band amplifier circuits have made a considerable progress recently (2 - 3), little achievement has been attained as for the mixer circuits.

This paper describes a work undertaken to design, fabricate and test the GaAs double-balanced dual-gate FET mixer IC for use in a front-end circuit of the UHF receivers.

DESIGN

A particular target that we aimed at is:

- 1) conversion gain: >5 dB

- 2) RF/LO feedthrough: <-20 dB

- 3) third-order intermodulation: <-55 dB.

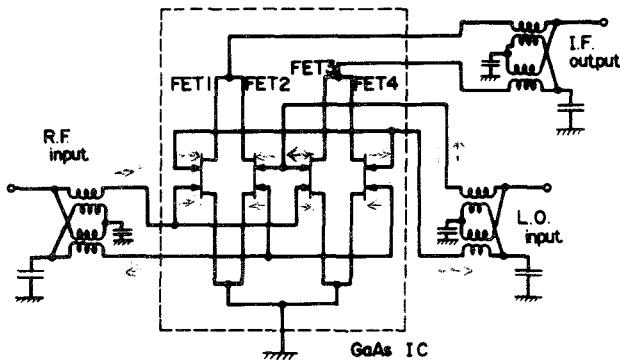

A double-balanced and dual-gate configuration was used for the present monolithic circuit design. The reasons are that the double-balanced configuration is essential for suppressing the RF/LO feedthrough and the dual-gate structure is suitable for avoiding cumbersome passive couplers.

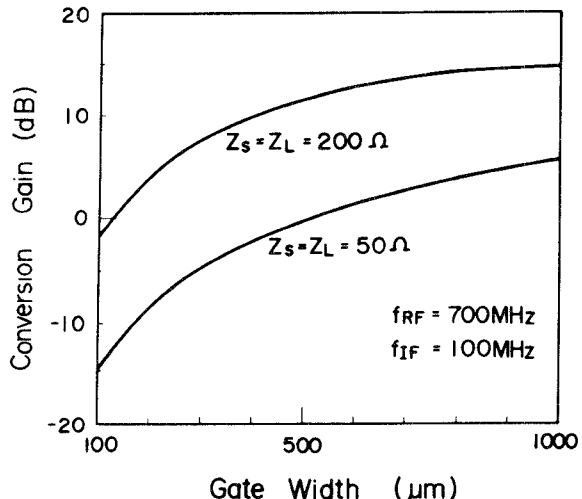

An analytical calculation of the conversion gain (4) of the dual-gate FET was carried out by using a simple model—cascode connection of two single-gate FET's (5). In Fig. 1, are shown the calculated results of the conversion gain as a function of the gate width  $W_g$  for the different Source/Load impedances  $Z_S$  and  $Z_L$ . The principal

single-gate FET parameters used in the calculation are:

source resistance;  $2.4 \times 10^3 \text{ Wg} [\Omega/\mu\text{m}]$

gate resistance;  $1.7 \times 10^{-2} \text{ x Wg} [\Omega \cdot \mu\text{m}]$

drain conductance;  $6.7 \times 10^{-6} \text{ x Wg} [S \cdot \mu\text{m}]$

gate-source capacitance;  $1.3 \times 10^{-3} \text{ x Wg} [\text{pF} \cdot \mu\text{m}]$ .

Despite designing the Source/Load impedances to be  $50\Omega$  is desirable for practical applications, the result of Fig. 1 indicates that use of  $50\Omega$  requires a large gate width  $W_g$  in order to satisfy the target conversion gain of 5 dB resulting in the increased power consumption and chip size. Therefore, we designed Source/Load impedances to be  $Z_S = Z_L = 200\Omega$  which requests use of the 1:4 balun. The calculated result of the conversion gain for  $Z_S = Z_L = 200\Omega$  informs that the target of 5 dB conversion gain can be satisfied by taking  $W_g = 300 \mu\text{m}$ .

The circuit diagram of the monolithic mixer IC is shown in Fig. 2. The RF and LO signals are applied to the first and second gates, respectively through the baluns. The IF signal is taken out also through the balun.

Fig. 1. Calculated conversion gain as a function of the gate width.

Fig. 2. Circuit diagram of the monolithic mixer IC.

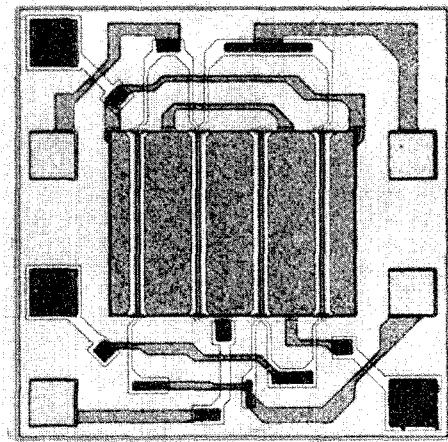

Fig. 3. Photograph of the completed mixer IC.

#### FABRICATION

The full ion-implantation process was used to fabricate the device. The n-type active and  $n^+$ -type contact layers were provided by selective ion implantation of Si onto an undoped LEC GaAs substrate under the condition of  $5 \times 10^{12} \text{ cm}^{-2}$  dose at 130 KeV and  $5 \times 10^{13} \text{ cm}^{-2}$  dose at 150 KeV, respectively. AuGe/Ni/Au and Ti/Al were used for the Ohmic contacts and the Schottky gate, respectively. The gate width of each FET was  $300 \mu\text{m}$  as previously mentioned and the gate length was  $1 \mu\text{m}$ . A photograph of the completed mixer IC is shown in Fig. 3. The chip size is  $750 \mu\text{m} \times 750 \mu\text{m}$ .

#### TEST RESULTS

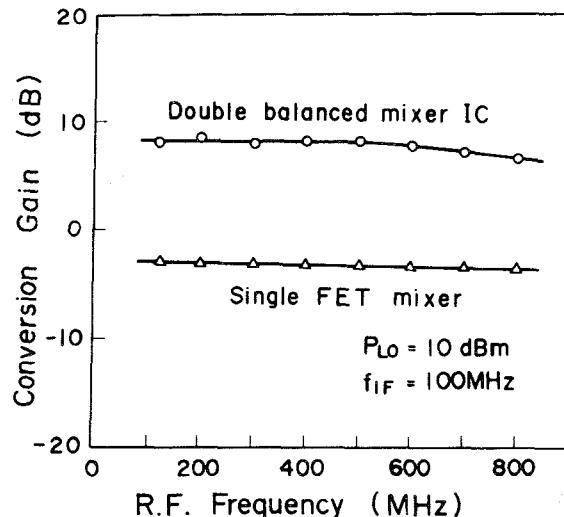

In Fig. 4, is shown the conversion gain of the experimental IC as a function of the RF

Fig. 4. Conversion gain of the experimental IC as a function of the RF frequency.

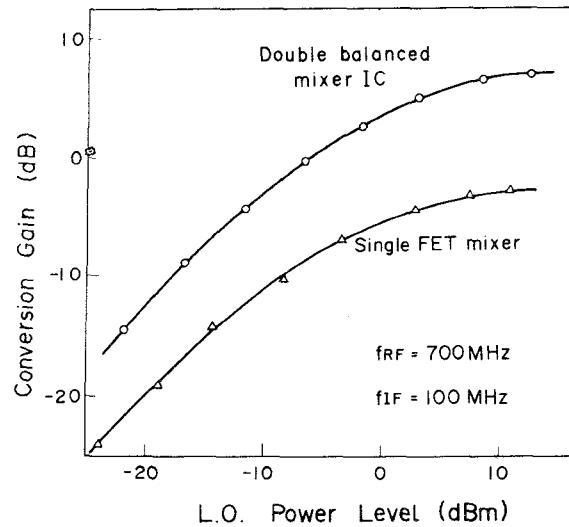

Fig. 5. Conversion gain of the experimental IC as a function of the LO power.

frequency. The IF frequency is fixed to be 100 MHz. RF and LO levels are  $-20 \text{ dBm}$  and  $10 \text{ dBm}$ , respectively. The results of the single FET mixer with the same dimension are also shown in Fig. 4 for comparison. Fig. 5 shows the conversion gain as a function of the LO power. It is found that the experimental device exhibits a very high conversion gain of  $6 - 8 \text{ dB}$  over a wide frequency range from 100 MHz to 800 MHz being very close to the values predicted by the design theory shown in Fig. 1. It is also noted that these high conversion gain is attained without additional matching circuits.

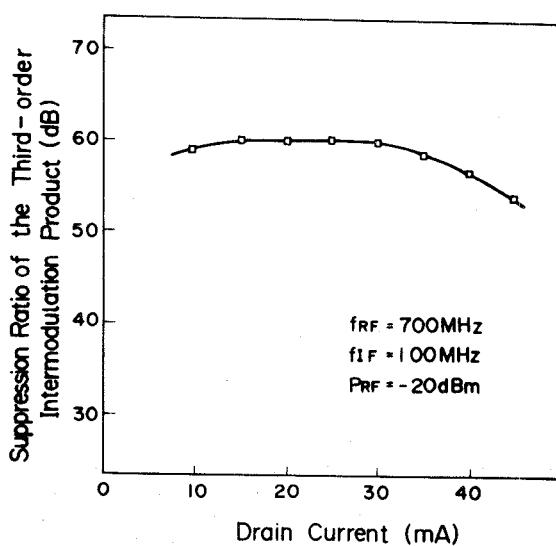

Fig. 6. Suppression ratio of the third-order intermodulation product as a function of the drain current.

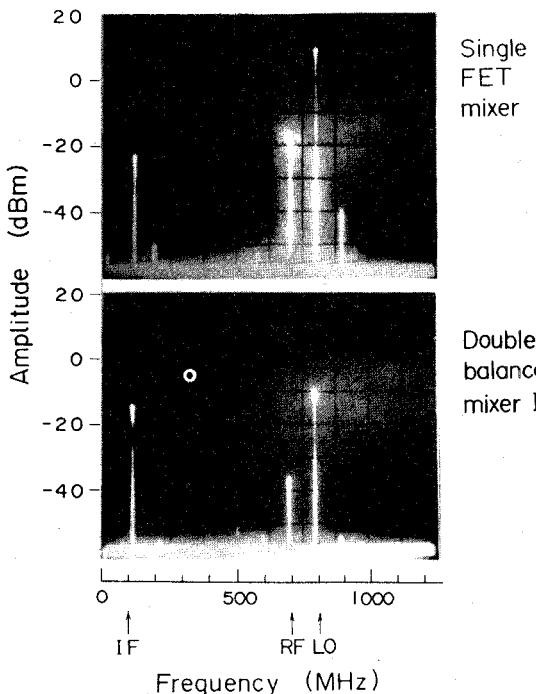

Fig. 7. Output frequency spectrum of the experimental IC comparing with that of the single FET mixer:  $P_{LO} = 10$  dBm,  $P_{RF} = -20$  dBm.

The measured suppression ratio of the third-order intermodulation product  $IM_3$  is shown in Fig. 6 where the RF signal at 700 MHz and the interference signal at 701 MHz are both -20 dBm and LO signal is 10 dBm. It is seen that the  $IM_3$  at 101 MHz is as high as 60 dB up to approximately 30 mA of the drain current.

The output frequency spectrum are shown in Fig. 7 comparing with that of the single FET mixer. It is obvious in this photograph that the RF and LO feedthrough's are well suppressed by more than 20 dB.

#### CONCLUSION

It is shown that the GaAs monolithic double-balanced dual-gate mixer IC has been developed, for the first time, exhibiting 6 - 8 dB conversion gain without matching over a wide frequency range from 100 MHz to 800 MHz with the extremely suppressed feedthrough and the intermodulation products.

#### ACKNOWLEDGMENT

The authors wish to thank M. Hagio and Dr. H. Mizuno for their constant encouragement throughout this study.

#### REFERENCES

- (1) U. Ablassmeier, W. Kellner, and H. Kniepkamp, "GaAs FET up convertor TV tuner," IEEE Trans. Electron Devices, vol. ED-28, no. 2, pp.1156-1159, Feb. 1980.

- (2) M. Nishiuma, S. Nambu, M. Hagio, and G. Kano, "A GaAs monolithic low-noise wideband amplifier," in Int. Symp. GaAs and Related Compounds Dig., pp.425-430, 1981.

- (3) M. Nishiuma, S. Katsu, S. Nambu, M. Hagio, and G. Kano, "A 2.2 dB NF 30-1700 MHz feedback amplifier," in ISSCC Dig., pp.194-195, 1983.

- (4) R.A. Pucel, D. Masse, and R. Bera, "Performance of GaAs FET mixers at X-band," IEEE Trans. Microwave Theory Tech., vol. MTT-24, no. 6, pp.351-360, June 1976.

- (5) S. Asai, F. Murai, and H. Kodera, "GaAs dual-gate Schottky-barrier FET's for microwave frequencies," IEEE Trans. Electron Devices, vol. ED-22, no. 10, pp.897-904, Oct. 1975.